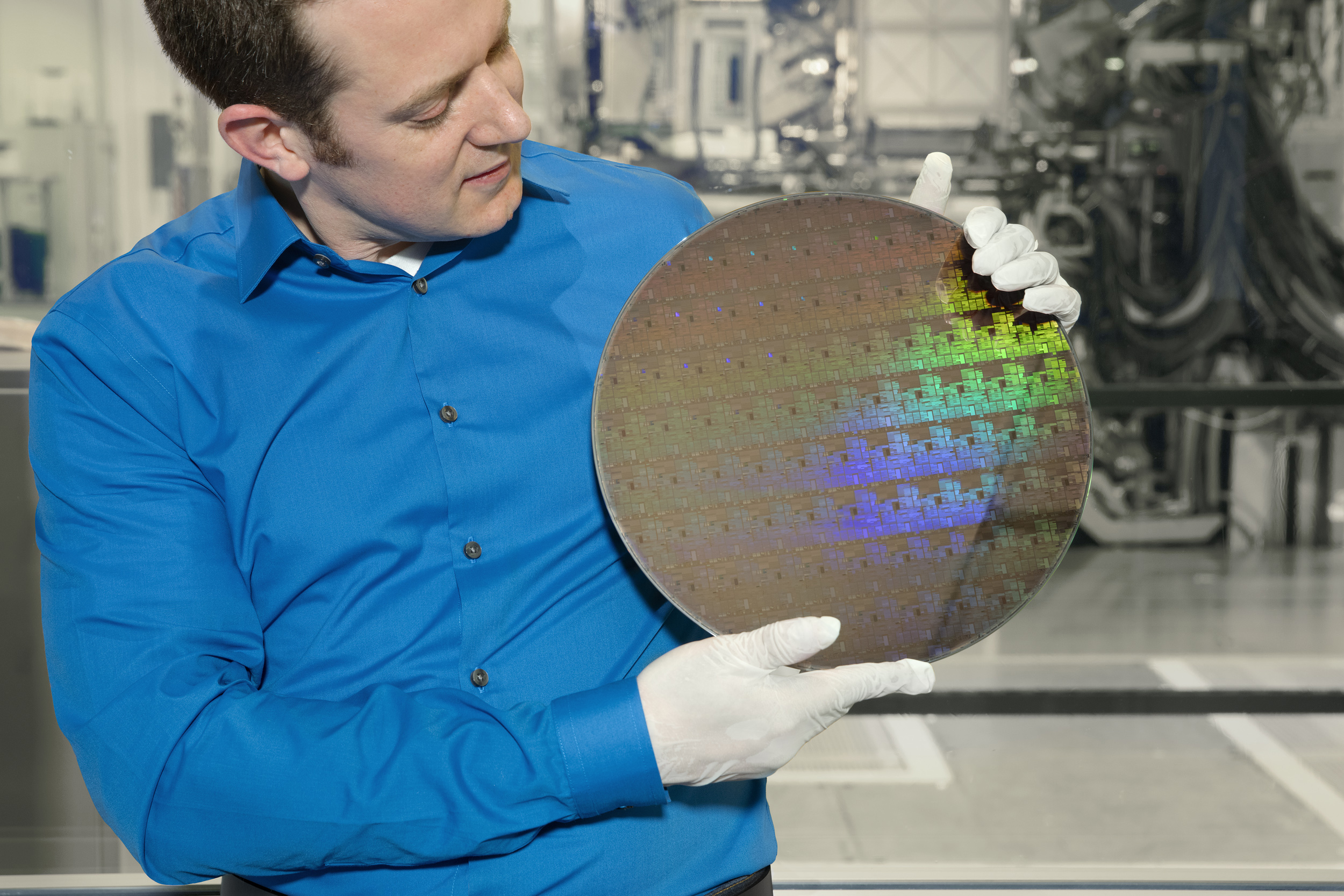

报道称,IBM公司用多年时间研究制制堆叠纳米芯片工艺手艺和材料,此前风行的电子束光刻工艺对于批量出产而言过于高贵,而即将投入出产的5纳米芯片,将利用工艺成本有所降低的极光紫外光刻手艺。新型芯片虽然只要指甲大小,其上却能集成300亿个晶体管,正在取10纳米芯片进行对比的测试中发觉,正在给定功率下,其机能可提拔40%;正在划一效率下,5纳米芯片能够节流74%电能。

IBM的半导体手艺和研究副总裁马克斯·凯尔暗示,“我们认为新布局将成为继finFET之后的遍及布局”,它代表了晶体管的将来。

摩尔定律正在二十年前就被唱衰,但曲到现正在,半导体工程师们仍然发扬钉子精力,从方寸地腾出无限空间。就仿佛水力压裂法能够从看似无价值的岩石中海量天然气,新半导体工艺仍正在硅片上大有用武之地。下逛消费计较力的人也应爱惜驯良用芯片,让手机和电脑成为我们的好帮手,而不是麻烦制制者。

半导体行业一曲努力于打制5纳米节点替代方案。IBM此次颁布发表的最新布局中,每个晶体管由三层堆叠的程度薄片构成,每片只要几纳米厚度,完全被栅极包抄,能防止电子泄露并节流电力,被称为“全包抄门”布局。

IBM打算取三星公司及全球制制商配合合做,出产5纳米节点测试芯片,并供给给全球客户,正在将来几年内满脚日益增加的市场需求,为从动驾驶、人工智能和5G收集的实现铺。

总编纂圈点

目前最先辈的晶体管是finFET,以芯片概况投射的载硫硅片翅片状隆起而定名,其性冲破的环节正在于,正在三维布局而非二维平面上电流的传送。这种设想可使用于10纳米以至7纳米节点芯片。可是,跟着芯片尺寸越来越小,电流变得愈起事以封闭,即便利用这种先辈的三面“门”布局,仍会发生电子泄露。

科技日报6月6日电(记者房琳琳)IBM日前正在日本京都颁布发表,该公司研究团队正在晶体管的制制上取得了庞大的冲破——正在一个指甲大小的芯片上,从集成200亿个7纳米晶体管飞跃到了300亿个5纳米晶体管。据美国电气和电子工程师协会(IEEE)《光谱》6日报道,这一超卓表示无望接近极限的摩尔定律,使电子元件继续朝着更小、更经济的标的目的成长。